Quick Start¶

In this quick start, we will show you how to:

Load a foundry Process Design Kit (PDK) in PhotonForge

Load PDK components

Run FDTD simulation by converting 2D layout files to 3D for electromagnetic simulations in a single line of code

Step 1: Loading a Foundry PDK¶

Start by importing numpy, photonforge, and siepic pdk library

[1]:

import numpy as np

import photonforge as pf

import siepic_forge as siepic_pdk

Select the open source ebeam process node, also called the technology stack

[2]:

# load the technology and set is as the default

technology = siepic_pdk.ebeam()

pf.config.default_technology = technology

[3]:

technology

[3]:

Name: SiEPIC EBeam

Version: 0.4.32

Layers

| Name | Layer | Description | Color | Pattern |

|---|---|---|---|---|

| Si | (1, 0) | Waveguides | #ff80a818 | \\ |

| PinRec | (1, 10) | SiEPIC | #00408018 | / |

| PinRecM | (1, 11) | SiEPIC | #00408018 | / |

| Si_Litho193nm | (1, 69) | Waveguides | #cc80a818 | \ |

| Waveguide | (1, 99) | Waveguides | #ff80a818 | \ |

| Si slab | (2, 0) | Waveguides | #80a8ff18 | / |

| SiN | (4, 0) | Waveguides | #a6cee318 | \\ |

| Oxide open (to BOX) | (6, 0) | Waveguides | #ffae0018 | \ |

| Text | (10, 0) | #0000ff18 | \ | |

| M1_heater | (11, 0) | Metal | #ebc63418 | xx |

| M2_router | (12, 0) | Metal | #90857018 | xx |

| M_Open | (13, 0) | Metal | #3471eb18 | xx |

| Si N | (20, 0) | Doping | #7000ff18 | \\ |

| Si N++ | (24, 0) | Doping | #0000ff18 | : |

| VC | (40, 0) | Metal | #3a027f18 | xx |

| DevRec | (68, 0) | SiEPIC | #00408018 | hollow |

| FbrTgt | (81, 0) | SiEPIC | #00408018 | / |

| FloorPlan | (99, 0) | Misc | #8000ff18 | hollow |

| SEM | (200, 0) | Misc | #ff00ff18 | \ |

| Deep Trench | (201, 0) | Misc | #c0c0c018 | solid |

| Keep out | (202, 0) | Misc | #a0a0c018 | // |

| Isolation Trench | (203, 0) | Misc | #c0c0c018 | solid |

| Dicing | (210, 0) | Misc | #a0a0c018 | solid |

| Chip design area | (290, 0) | Misc | #80005718 | hollow |

| FDTD | (733, 0) | SiEPIC | #80005718 | hollow |

| BlackBox | (998, 0) | SiEPIC | #00408018 | solid |

| Errors | (999, 0) | SiEPIC | #00008018 | / |

Extrusion Specs

| # | Mask | Limits (μm) | Sidewal (°) | Opt. Medium | Elec. Medium |

|---|---|---|---|---|---|

| 0 | 'Oxide open (to BOX)' | 0, inf | 0 | Medium(permittivity=1.0) | Medium(permittivity=1.0) |

| 1 | 'Si' | 0, 0.22 | 0 | cSi_Li1993_293K | Si |

| 2 | 'Si slab' | 0, 0.09 | 0 | cSi_Li1993_293K | Si |

| 3 | 'SiN' | 0, 0.4 | 0 | Si3N4_Luke2015_PMLStable | Si3N4 |

| 4 | 'M2_router' +…… 'M1_heater' | 2.42, 2.62 | 0 | W_Werner2009 | LossyMetalMedium……(frequency_range=(100000000.0, 200000000000.0), conductivity=1.6, fit_param={'attrs': {}, 'max_num_poles': 16, 'tolerance_rms': 0.001, 'frequency_sampling_points': 20, 'log_sampling': True, 'type': 'SurfaceImpedanceFitterParam'}) |

| 5 | 'M2_router' | 2.62, 3.02 | 0 | Au_Olmon2012evaporated | LossyMetalMedium……(frequency_range=(100000000.0, 200000000000.0), conductivity=17.0, fit_param={'attrs': {}, 'max_num_poles': 16, 'tolerance_rms': 0.001, 'frequency_sampling_points': 20, 'log_sampling': True, 'type': 'SurfaceImpedanceFitterParam'}) |

| 6 | 'M_Open' | 3.02, inf | 0 | Medium(permittivity=1.0) | Medium(permittivity=1.0) |

| 7 | 'Deep Trench' +…… 'Isolation Trench' + 'Dicing' | -inf, inf | 0 | Medium(permittivity=1.0) | Medium(permittivity=1.0) |

Ports

| Name | Classification | Description | Width (μm) | Limits (μm) | Radius (μm) | Modes | Target n_eff | Path profiles (μm) | Voltage path | Current path |

|---|---|---|---|---|---|---|---|---|---|---|

| MM_SiN_TE_1550_3000 | optical | Multimode SiN Strip TE 1550 nm,…… w=3000 nm | 8 | -2.5, 2.9 | 0 | 7 | 2.1 | 'SiN': 3 | ||

| MM_TE_1550_2000 | optical | Multimode Strip TE 1550 nm,…… w=2000 nm | 6 | -2, 2.22 | 0 | 12 | 3.5 | 'Si': 2 | ||

| MM_TE_1550_3000 | optical | Multimode Strip TE 1550 nm,…… w=3000 nm | 6 | -2, 2.22 | 0 | 17 | 3.5 | 'Si': 3 | ||

| Rib_TE_1310_350 | optical | Rib (90 nm slab) TE 1310 nm,…… w=350 nm | 2.35 | -1, 1.22 | 0 | 1 | 3.5 | 'Si': 0.35, 'Si…… slab': 3 | ||

| Rib_TE_1550_500 | optical | Rib (90 nm slab) TE 1550 nm,…… w=500 nm | 2.5 | -1, 1.22 | 0 | 1 | 3.5 | 'Si': 0.5, 'Si…… slab': 3 | ||

| SiN_TE-TM_1550_1000 | optical | SiN Strip TM 1550 nm, w=1000 nm | 3 | -1.5, 1.9 | 0 | 2 | 2.1 | 'SiN': 1 | ||

| SiN_TE_1310_750 | optical | SiN Strip TE 1310 nm, w=750 nm | 3 | -1, 1.4 | 0 | 1 | 2.1 | 'SiN': 0.75 | ||

| SiN_TE_1310_800 | optical | SiN Strip TE 1310 nm, w=800 nm | 3 | -1, 1.4 | 0 | 1 | 2.1 | 'SiN': 0.8 | ||

| SiN_TE_1550_1000 | optical | SiN Strip TE 1550 nm, w=1000 nm | 3 | -1, 1.4 | 0 | 1 | 2.1 | 'SiN': 1 | ||

| SiN_TE_1550_750 | optical | SiN Strip TE 1550 nm, w=750 nm | 3 | -1, 1.4 | 0 | 1 | 2.1 | 'SiN': 0.75 | ||

| SiN_TE_1550_800 | optical | SiN Strip TE 1550 nm, w=800 nm | 3 | -1, 1.4 | 0 | 1 | 2.1 | 'SiN': 0.8 | ||

| SiN_TE_895_450 | optical | SiN Strip TE 895 nm, w=450 nm | 2 | -1, 1.4 | 0 | 1 | 2.1 | 'SiN': 0.45 | ||

| SiN_TM_1310_750 | optical | SiN Strip TM 1310 nm, w=750 nm | 3 | -1.5, 1.9 | 0 | 1 + 1 (TM) | 2.1 | 'SiN': 0.75 | ||

| SiN_TM_1550_1000 | optical | SiN Strip TM 1550 nm, w=1000 nm | 3 | -1.5, 1.9 | 0 | 1 + 1 (TM) | 2.1 | 'SiN': 1 | ||

| Slot_TE_1550_500 | optical | Slot TE 1550 nm, w=500 nm,…… gap=100nm | 2 | -1, 1.22 | 0 | 1 | 3.5 | 'Si': 0.2 (-0.15),…… 'Si': 0.2 (+0.15) | ||

| TE-TM_1550_450 | optical | Strip TE-TM 1550, w=450 nm | 2 | -1, 1.22 | 0 | 2 | 3.5 | 'Si': 0.45 | ||

| TE_1310_350 | optical | Strip TE 1310 nm, w=350 nm | 2 | -1, 1.22 | 0 | 1 | 3.5 | 'Si': 0.35 | ||

| TE_1310_410 | optical | Strip TE 1310 nm, w=410 nm | 2 | -1, 1.22 | 0 | 1 | 3.5 | 'Si': 0.41 | ||

| TE_1550_500 | optical | Strip TE 1550 nm, w=500 nm | 2 | -1, 1.22 | 0 | 1 | 3.5 | 'Si': 0.5 | ||

| TM_1310_350 | optical | Strip TM 1310 nm, w=350 nm | 2 | -1, 1.22 | 0 | 1 + 1 (TM) | 3.5 | 'Si': 0.35 | ||

| TM_1550_500 | optical | Strip TM 1550 nm, w=500 nm | 2.5 | -1, 1.22 | 0 | 1 + 1 (TM) | 3.5 | 'Si': 0.5 | ||

| eskid_TE_1550 | optical | eskid TE 1550 | 3.31 | -1, 1.22 | 0 | 1 | 3.5 | 'Si': 0.35,…… 'Si': 0.06 (+0.265), 'Si': 0.06 (-0.265), 'Si': 0.06 (+0.385), 'Si': 0.06 (-0.385), 'Si': 0.06 (+0.505), 'Si': 0.06 (-0.505), 'Si': 0.06 (+0.625), 'Si': 0.06 (-0.625) |

Background medium

- Optical: SiO2_Palik_Lossless

- Electrical: SiO2

Connections: []

[4]:

technology.random_variables

[4]:

[RandomVariable('si_thickness', **{'value': 0.22, 'stdev': 0.0037166666666666667}),

RandomVariable('bottom_oxide_thickness', **{'value': 3.017, 'stdev': 0.001})]

Step 2: Loading foundry provided PDK components¶

[5]:

cross = siepic_pdk.component("crossing_horizontal")

cross

[5]:

[6]:

cross.models

[6]:

{'Tidy3D': Tidy3DModel(run_time=None, medium=None, symmetry=(0, 0, 0), boundary_spec=None, monitors=(), structures=(), grid_spec=None, shutoff=None, subpixel=None, courant=None, port_symmetries=[('P0', 'P1', {'P1': 'P0', 'P2': 'P3', 'P3': 'P2'}), ('P0', 'P2', {'P1': 'P3', 'P2': 'P0', 'P3': 'P1'}), ('P0', 'P3', {'P1': 'P2', 'P2': 'P1', 'P3': 'P0'})], bounds=((None, None, None), (None, None, None)), source_gap=None, simulation_updates={}, verbose=True)}

Step 3: Covert 2D layout files to 3D for electromagnetic simulations¶

[7]:

# run 3D fdtd simulation to compute s_matrix

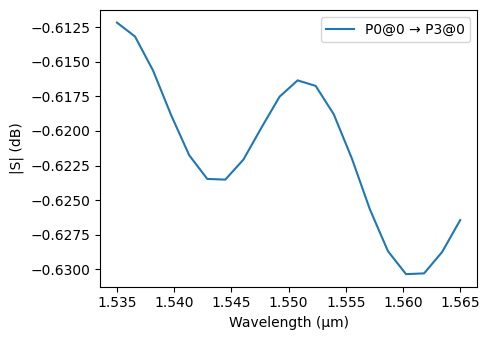

wavelengths = np.linspace(1.535, 1.565, 20)

s_matrix = cross.s_matrix(frequencies = pf.C_0/wavelengths)

Loading cached simulation from .tidy3d/pf_cache/PGK/fdtd_info-QTFDG6OIXZLQB3FCM6SX6BCT7LOIK4WYHCQHQRF6OAORTXFICM7Q.json.

Progress: 100%

[8]:

plt = pf.plot_s_matrix(s_matrix, y="dB", input_ports= ["P0"], output_ports = ["P3"])